Xilinx ISE v14.7 破解版

- 软件介绍

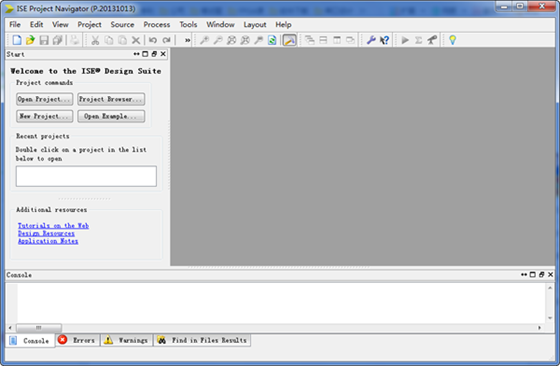

- 软件截图

- 相关文章

Xilinx ISE是一款很厉害的硬件设计软件,在这款Xilinx ISE软件中有很多的功能是我们可以去使用的,在有了这些功能之后就可以更好的帮助我们去设计出出色的硬件产品,,并且在这款工具中还拥有专业的PLD设计环境,在这样的设计环境中使我们的开发人员在进行设计硬件的时候更加的方便快捷,支持进行重复设计,是我们的用户在进行调试的时候更加的准确,还支持在多台计算机上进行分布式的处理,需要这款工具的用户就来下载吧!

Xilinx ISE优势:

Xilinx Platform Studio (XPS) –对于适配到Xilinx FPGA的采用PowerPC 硬处理器核和 Xilinx MicroBlaze 软处理器核的嵌入式子系统,Xilinx Platform Studio套件可以完成设计的简化、抽象和加速。XPS 套件与计算IP库、软驱动、文档、参考设计和MicroBlaze软处理器IP内核共同构成赛灵思嵌入式开发套件(EDK)的一部分。

PlanAhead设计和分析工具 – 通过采用过去ASIC设计人员常用的分层布局规划技术来提高综合和布局布线等设计步骤的效率,PlanAhead工具支持FPGA设计人员取得更优异的结 果。这一方法可大大减少设计反复次数和缩短反复时间,并且平均可将设计性能再提高15%。PlanAhead用户可快速通过“what if”假设分析来尽早确定并排除潜在问题,同时将关键路径和模块分组并通过连接分析和利用率控制来提高布通率。

ChipScope Pro调试和验证 –ChipScope™ Pro分析工具支持对FPGA设计进行片上实时验证和调试,器件此时仍然与整个系统互动。与传统调试方法相比,可以使验证周期缩短50%。 ChipScope Pro还可以直接与Agilent逻辑分析仪配合使用,实现更深的FPGA信号分析。

ISE Simulator -ISE Simulator提供了与ISE环境集成的完整的全功能HDL仿真工具。ISE Simulator有两个版本。ISE Simulator Lite随所有版本ISE免费提供,为HDL源代码不超过1万行的CPLD和低密度FPGA设计提供了一个理想的解决方案。ISE Simulator完全版支持所有设计密度,可做为ISE Foudation的低成本附加模块提供。

ModelSim Xilinx Edition III –ModelSim XE III是完整的PC硬件描述语言(HDL)仿真和调试环境,支持设计人员完成HDL源代码、功率以及时序模型的验证。MXE III 提供了 100%和 VHDL和Verilog语言覆盖,提供了源代码察看器/编辑器、波形察看器、设计结构浏览器、列表窗口以及其它功能来提高生产力。

Xilinx ISE说明:

针对 VIRTEX -6 和 SPARTAN -6 FPGA:

借助 Xilinx ISE Design Suite 的突破性技术提高系统级设计效率并加快产品投产。 ISE Design Suite 采用各种方法来实现团队设计、功耗优化以及简化 IP 集成,从而分发挥 Xilinx 目标设计平台在配置逻辑、嵌入式和 DSP 设计方面的潜力 - 所有这一切均可通过紧密集成的设计流程来实现。

利用自动时钟门控技术将动态功耗降低30%之多

利用第四代部分重配置设计流程降低系统成本

PlanAhead - 面向逻辑设计人员的新款 RTL 到比特流设计流程

利用 AXI4 接口实现即插即用式 FPGA 设计

Xilinx ISE操作:

1、下载文件找到"Setup.exe"双击运行,进入软件安装向导界面;

2、进入软件的安装向导界面,点击Next;

3、点击我同意软件的许可协议,点击Next;

4、选择用户需要进行安装的产品,点击Next;

5、选择需要进行安装的组件,如果您不知道需要安装那个组件,就选择全部进行安装,点击Next;

6、选择软件安装的位置,建议安装在D盘,点击Next;

7、软件已经准备好了进行安装,不过安装需要15G,您注意自己的磁盘空间,点击Next;

8、正在进行安装中,请大家耐心的等待.可能比较的久..........

9、安装到一半的时候,需要进行组件的安装,

10、点击Install组件已经准备好了进行安装;

11、组件已经安装完成,点击Finish;

12、软件已经安装完成,点击Finish;

Xilinx ISE评价:

使用高密度脂蛋白编码器程序Xilinx fpga

使用高密度脂蛋白编码器,可以自动生成Xilinx fpga的硬件描述语言(VHDL)和Verilog代码从MATLAB,模型,和Stateflow模型。这种方法支持各种系统对象中可用的产品,如通信系统工具箱和DSP系统工具箱。

程序Xilinx fpga使用HDL编码器和Xilinx系统发电机

HDL编码支持模型的代码生成模型构造块的组合模型和Xilinx-specific blocksets从系统发电机。高密度脂蛋白编码器的系统发电机子系统块使您能够包括模型建立与仿真软件系统发电机子系统。HDL编码器使用系统子系统的发生器来生成代码块和集成的完整设计成synthesizeable高密度脂蛋白。

程序Xilinx Zynq SoC设备嵌入式编码器和高密度脂蛋白编码器

与基于模型的设计,设计团队可以完成系统模拟模型和使用C / c++和HDL代码生成从模型到目标Xilinx zynq - 7000可编程SoC设备,提供组合臂®皮层®a9核心以及传统Xilinx FPGA的可编程逻辑。

猜您喜欢

换一换软件TOP榜

-

125.76MB

1 -

3.63GB

2 -

2.3G

3 -

3.41MB

4 -

3.58MB

5 -

727.3MB

6 -

100MB

7 -

18.33MB

8